# W600 Hardware Design Guide V1.0.0

Beijing Winner Microelectronics Co., Ltd. (Winner Micro) Addr: 18<sup>th</sup> Floor, Yindu Building, 67<sup>th</sup> Fucheng Road, Haidian District, Beijing, P.R.Chian Tel: +86-10-62161900 Company Website: www.winnermicro.com

## **Document History**

| Version | Completion Date | Revision Record | Author | Auditor | Approver |

|---------|-----------------|-----------------|--------|---------|----------|

| V1.0.0  | 2018-10-25      | Initial release | Linda  | Ray     | WM       |

|         |                 |                 |        |         |          |

|         |                 |                 |        |         |          |

|         |                 |                 |        |         |          |

|         |                 |                 |        |         |          |

### Content

| 1 | Overv | view      |                             |

|---|-------|-----------|-----------------------------|

| 2 | Pin D | escriptio | on1                         |

| 3 | Perip | hery Cir  | cuit Design of W600         |

|   | 3.1   | RE        | SET Circuit Design          |

|   | 3.2   | Ref       | erence Clock Circuit Design |

|   | 3.3   | RF        | Circuit Design              |

|   | 3.4   |           | IO Design                   |

|   | 3.5   | Pov       | ver Circuit Design          |

|   | 3.6   | GN        | D Design 6                  |

|   | 3.7   | Ant       | enna Design                 |

|   |       | 3.7.1     | External antenna            |

|   |       | 3.7.2     | PCB antenna                 |

|   |       |           |                             |

#### 1 Overview

W600 integrates ARM CPU, rich peripheral interfaces, Wi-Fi MAC, Baseband, Security, RF. The chipset has rich functions and can meet the hardware requirement for IoT products. W600 is QFN32 package with the size 5mm x 5mm. Very few circuit devices are needed for the peripheral of the chip and a module can be designed with very small size. This design guide has introduced pin definition, physical size, timer, power, RF circuit and antenna etc. When customers begin to design products with W600, please strictly follow this guide, so as to get the best RF performance.

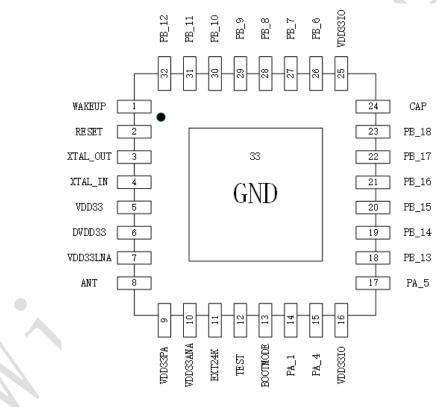

2 Pin Description

Figure 2-1 QFN32 Pin Diagram

# Beijing Winner Microelectronics Co., Ltd.

#### Table 2-1 Pin Description

| Pin No.  | Pin Name | Туре | Function Description           | Multi-function                                                 |

|----------|----------|------|--------------------------------|----------------------------------------------------------------|

| i in no. |          | туре | after reset                    |                                                                |

| 1        | WAKEUP   | т    | WAKEUP(wake up chipset         |                                                                |

| 1        | WAKEUP   | Ι    | by high level power)           |                                                                |

| 0        | DECET    | т    | RESET(reset chipset by         |                                                                |

| 2        | RESET    | Ι    | low level power)               |                                                                |

| 3        | XTAL-OUT | 0    | Output External                |                                                                |

| 5        | ATAL OUT | 0    | crystal oscillator             |                                                                |

| 4        | XTAL-IN  | Ι    | input External crystal         |                                                                |

| Ţ        | AIAL IN  | T    | oscillator                     |                                                                |

| 5        | VDD33    | Р    | power supply, 3.3V             |                                                                |

| 6        | DVDD33   | Р    | power supply for               |                                                                |

| 0        | DTDD00   | 1    | digital circuit, 3.3V          |                                                                |

| 7        | VDD33LNA | Р    | power supply for LNA,          |                                                                |

| 1        | VDD03ENA | 1    | 3. 3V                          | Y                                                              |

| 8        | ANT      | I/P  | RF antenna                     |                                                                |

| 9        | VDD33PA  | Р    | PA power supply, 3.3V          |                                                                |

| 10       | VDD33ANA | Р    | power supply for               |                                                                |

| 10       | VDDOOMM  | 1    | analog circuit, 3.3V           |                                                                |

| 11       | EXT24K   | р    | series connect with a          |                                                                |

| 11       |          |      | resistor $(24K \Omega + -1\%)$ |                                                                |

| 12       | TEST     | Ι    | Test mode                      |                                                                |

| 13       | PA_0     | I/0  | BOOTMODE                       | UART2_RX、PWM_1、GPIOPA_0                                        |

| 14       | PA1      | I/0  | Reserved                       | SIM_DATA、 PWM_2、 SPI(M/S)_CK、                                  |

|          |          | 1/ 0 |                                | GPIOPA_1                                                       |

| 15       | PA4      | I/0  | UARTO_TX                       | <pre>PWM_5、SPI(M/S)_DO、I<sup>2</sup>S_M_SCL、</pre>             |

| 10       | 1 /1 1   | 1/ 0 |                                | GPIOPA_4                                                       |

| 16       | VDD33102 | Р    | IO power supply,3.3V           |                                                                |

| 17       | PA_5     | I/0  | UARTO_RX                       | <pre>PWM_1、SPI(M/S)_DI、I<sup>2</sup>S_M_EXTCLK、</pre>          |

| · ·      |          | 1, V |                                | GPIOPA_5                                                       |

| 18       | PB_13    | I/0  | PWM_2                          | I <sup>2</sup> C_SCL、SDIO_CMD、GPIOPB_13                        |

| 19       | PB_14    | I/0  | H_SPI_INT                      | <pre>PWM_5 、 I<sup>2</sup>C_DAT 、 I<sup>2</sup>S_S_SDA 、</pre> |

# Beijing Winner Microelectronics Co., Ltd.

|     | [        | <del></del> |                       |                                            |

|-----|----------|-------------|-----------------------|--------------------------------------------|

|     |          |             |                       | GPIOPB_14                                  |

| 20  | DD 15    | I/0         | U SDI CS              | PWM_4、SPI(M/S)_CS、I <sup>2</sup> S_S_SC    |

| 20  | PB_15    | 1/0         | H_SPI_CS              | GPIOPB_15                                  |

| 0.1 | DD 10    | т /о        | IL CDI. CV            | PWM_3、SPI(M/S)_CK、I <sup>2</sup> S_S_R     |

| 21  | PB_16    | I/0         | H_SPI_CK              | GPIOPB_16                                  |

| 0.0 | DD 17    | т./о        | IL CDI DI             | PWM_2、SPI(M/S)_DI、UART1_R                  |

| 22  | PB_17    | I/0         | H_SPI_DI              | GPIOPB_17                                  |

| 23  | DD 10    | I/0         | IL SDI DO             | PWM_1、SPI(M/S)_DO、UART1_T                  |

| 23  | PB_18    | 1/0         | H_SPI_DO              | GPIOPB_18                                  |

| 24  | CAP      | Ι           | Capacitance,1µF       |                                            |

| 25  | VDD33I01 | Р           | IO power supply, 3.3V |                                            |

| 26  | PB_6     | I/0         | Reserved              | SWDAT, UARTO_RX, PWM_4, SIM_0              |

| 20  | rd_0     | 1/0         | Reserved              | GPIOPB_6                                   |

| 27  | PB_7     | I/0         | Reserved              | SWCK 、 UARTO_TX 、 SDIO_CME                 |

| 21  | rD_(     | 1/0         | Reserved              | SPI(M/S)_CS、GPIOPB_7                       |

| 28  | PB_8     | I/0         | PWM 5                 | H_SPI_CK、 SDIO_CK、 I <sup>2</sup> S_M_SC   |

| 20  | TD_0     | 170         | rwm_0                 | GPIOPB_8                                   |

| 29  | DD O     | I/0         | UART1_CTS             | H_SPI_INT, SDIO_DATO, I <sup>2</sup> S_M_S |

| 29  | PB_9     | 1/0         | UARTI_CIS             | GPIOPB_9                                   |

| 30  | PB 10    | I/0         | UART1_RTS             | H_SPI_CS、SDIO_DAT1、I <sup>2</sup> S_M_F    |

| 30  | FD_10    | 1/0         | UARTI_RIS             | GPIOPB_10                                  |

| 31  | PB_11    | 1/0         | UADT1 DY              | H_SPI_DI、SDIO_DAT2、I <sup>2</sup> C_SC     |

| 51  | 1D_11    | 1/0         | UART1_RX              | GPIOPB_11                                  |

| 32  | PB_12    | I/0         | UART1_TX              | H_SPI_DO、SDIO_DAT3、I <sup>2</sup> C_DA     |

| 52  | 1 D_12   | 1/0         |                       | GPIOPB_12                                  |

| 33  | PAD      | GND         | Ground                |                                            |

#### 3 Periphery Circuit Design of W600

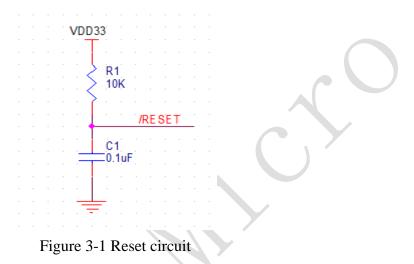

#### 3.1 RESET Circuit Design

Reset circuit is proposed to design with RC circuit. W600 resets automatically by low level power. If RESET pin controlled by external circuit, the chipset will reset when the level is below 2.0V. The low level needs to last more than 100µs. See Figure 3-1.

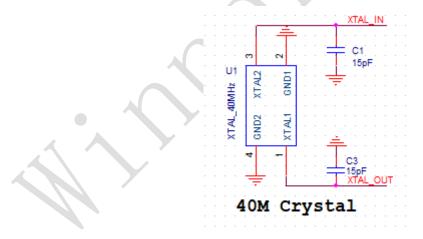

#### 3.2 Reference Clock Circuit Design

40MHz frequency is used for W600's reference clock which should be -40~85°C/ $\pm$  10ppm with 10pF load capacitance. See figure 3-2.

Figure 3-2 Crystal oscillator circuit

Clock routing is as close to the chip as possible, as short as possible, and leave away from interference source. All other routes are prohibited to be layed below the clock to prevent interference with clock source.

#### 3.3 RF Circuit Design

The chipset is designed with a single antenna. W600 integrates PA and transceiver switch.

The impedance of the antenna port is  $50\Omega$ . According to the performance requirement of module design, it is suggested to use  $\pi$  type design to match the circuit. External elements should be optimized according to the actual antenna impedance value.

In order to save cost, customers can use two-layer board design with FR-4 board and 0.8mm thickness. In order to achieve  $50\Omega$  of RF wiring impedance, the wire width should be 20mil, the distance from wire to copper should be 5mil. RF routing is on top layer. No other routing can be used on the back of RF routing, and copper should be covered the back of RF routing to ensure the integrity of RF reference GND.

#### 3.4 GPIO Design

After the chiset is power on, the pin15 and pin17 is default for UART0 port. Firmware downloading, AT+command and output debugging log can be used with this port. Customers should be careful not to use this port as GPIO if you want to use this port to download or debug. Ater the whole system is in operation, this port can be reused for other ports.

#### Table 3-2 UARTO Port Description

| 15 | PA4  | 1/0 | UARTO_TX |

|----|------|-----|----------|

| 17 | PA_5 | Ι/0 | UARTO_RX |

Other reused pins can refer to Table 2-1.

#### 3.5 Power Circuit Design

The input foot of the chip's power supply is equipped with the corresponding filter capacitor, and the total current of whole chip power supply is recommended to be 500mA or more. The wiring width shoude not be less than 30mil. The power supply range is 3.0V~3.6V. Over 3.6V may cause permanent damage to the chip. Lower than 3.0V may cause whole performance degradation. The reference design can see the following tables.

A 10µf and a 4.7nf fitler capacitors should be placed near pin5, pin6, pin7. See table 3-3.

#### Table 3-3 Power Pin Description

| 5 | VDD33    | Р | POWER, 3.3V                 |  |

|---|----------|---|-----------------------------|--|

| 6 | DVDD33   | Р | Digital circuit power, 3.3V |  |

| 7 | VDD33LNA | Р | LNA power, 3.3V             |  |

A 47µf filter capacitor should be placed near pin9 and pin10. We suggest customer to place a

330µf electrolytic capacitor on their base board. See table 3-4.

#### Table 3-4 Power PIN Description

| 9  | VDD33PA  | Р | PA power, 3.3V     |  |

|----|----------|---|--------------------|--|

| 10 | VDD33ANA | Р | Analog power, 3.3V |  |

Pin24 need an external 1µf filter capacitor.

Pin11 need an external 24K resistance with the accuracy 1%.

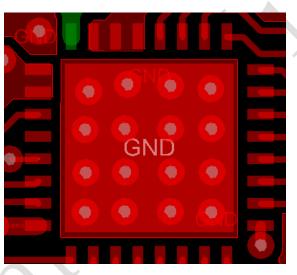

#### 3.6 GND Design

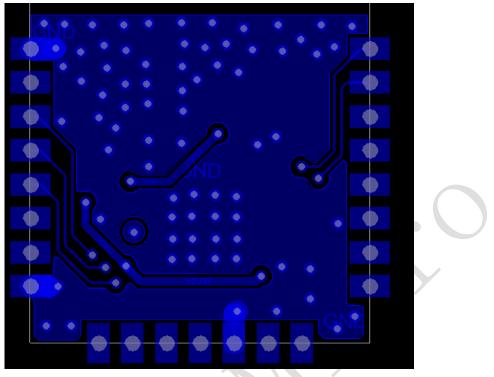

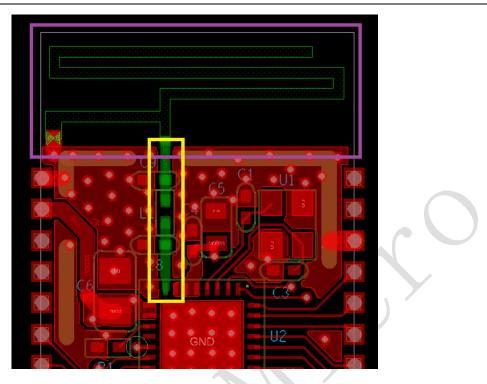

The PAD in the middle of W600 is for heat sinking and has to connect with GND and need to add drilling. See figure 3-3 and figure 3-4

Figure 3-3 GND design

After the product design is completed, it needs all layers PCB to be copper-coated grounding treatment, and let as few as possible routing go though the back of the chip.

Beijing Winner Microelectronics Co., Ltd.

Figure 3-4 GND design

#### 3.7 Antenna Design

Both external antenna and PCB antenna can be used for module design.

#### 3.7.1 External antenna

The connecting seat of the external antenna is as far away as possible from the noise sources such as the power interference from bottom board power and other noice souces.

#### 3.7.2 PCB antenna

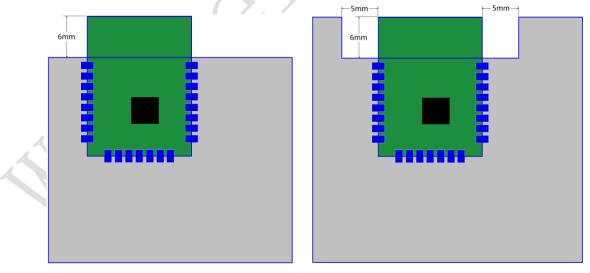

The design of PCB antenna should be strictly in accordance with this user guide to prevent antenna performance degradation. Copper coating on the back of the antenna should be hollowed out. The antenna reference ground should be as large as possible. The PCB antenna should be simulated in practice. The antenna size map should be imported into module PCB after simulation. All layers of antenna area can not be covered with copper. See figure 3-5.

### Beijing Winner Microelectronics Co., Ltd.

Figure 3-5 PCB antenna design

Figure 3-6 and 3-7 are 2 antenna placement modes which can add very little effect on performance of antenna. We suggest customers to choose one of these 2 modes to design the placement. For the second placement mode, PCB antenna should be at least 5.0mm from both sides of the bottom board.

Figure 3-6